Sharp CE-158 Instrukcja Użytkownika Strona 18

- Strona / 36

- Spis treści

- BOOKMARKI

Oceniono. / 5. Na podstawie oceny klientów

All and more about Sharp PC-1500

at

http:f/www.PC-1500.info

~•rr

-;

TP9

~

~~~~~~~~~~~

~~

~tnsr

_;

;._

tTAS

-:

ASEL

~~~~~~~~~

v-~

~~~

-1

•~~~...,._

~--..,

;,...-~~

~~

II

* READ IS

THE

OVERLAP

OF

CS

!.

CS3. RD/WR • I AND CS2 • 0

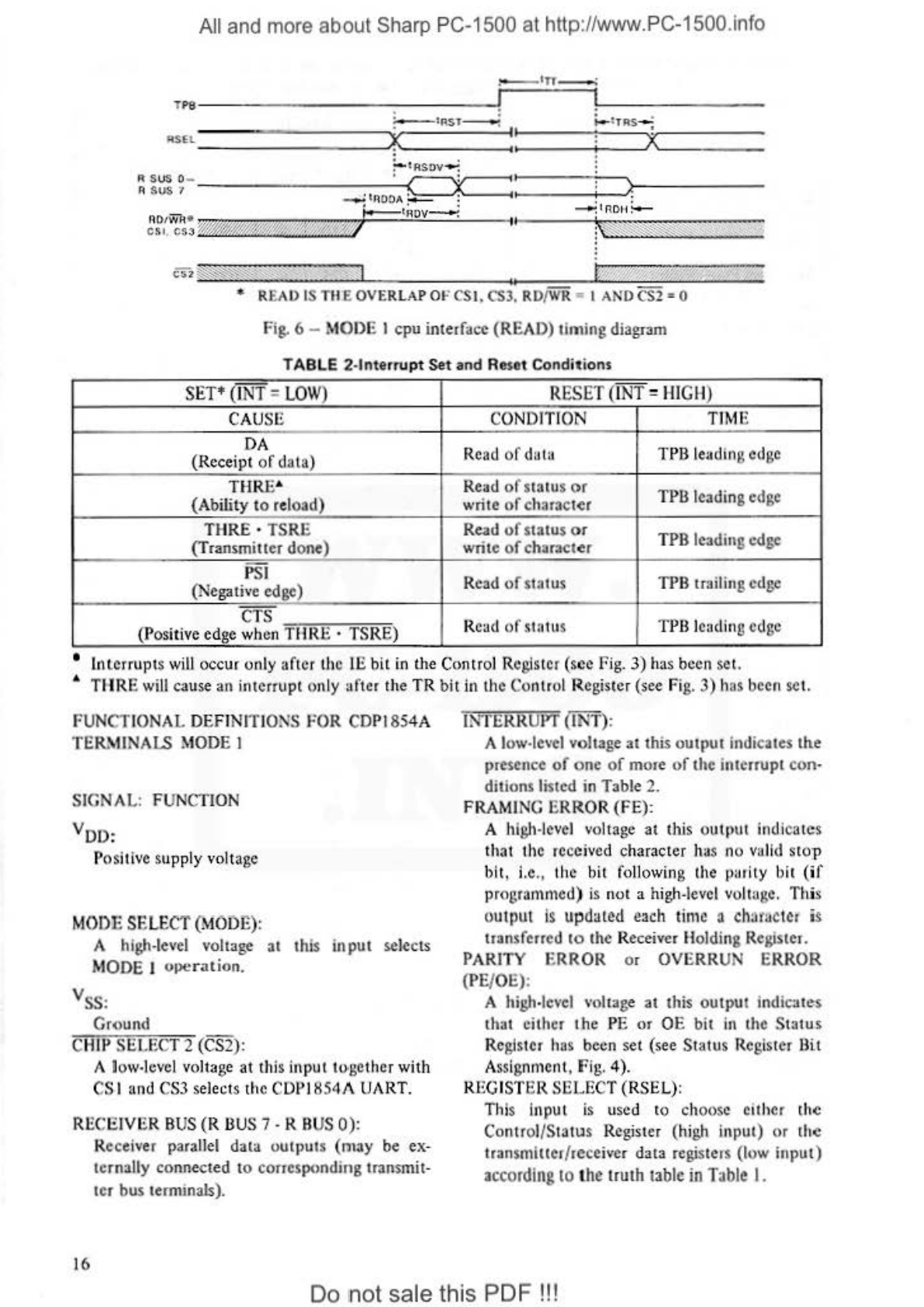

Fig. 6 - MODE I

cpu

inte1facc (READ) timing diagram

TABLE 2·1nte

rrupt

Set

and Reset Cond

iti

ons

SET

*

(I

NT =

LOW)

RESET

(INT

=

HIGll

)

CAUSE

CONDITION TIME

DA

Re

ad

of

datn TPB leading edge

(Receipt of dat

a}

THR

E* Read

or

Stntus

or

TPB leading edge

(Ability

to

reload) write

of

chara

cter

THRE

•

TSRE

Read

of

status

or

TPB leading edge

(Transmitter

done)

write

of

character

PSI

Read

of

status

TPB trailing edge

(Negat

ive

edge)

CTS

Read

of

st

:i

t us

TPB leading edge

(Positive

edge wh

en

TH RE ·

TSRE

)

•

Int

err

up

ts will occur only

af

t

er

lhe

1£

b

it

in the Control R

cg

islcr

(se

c Fi

g.

3) has been set.

• TH

RE

will

cause an inter

rupt

on

ly

:a

fter the

TR

bit in

th

e Co

nt

ro

l Register (see Fig. 3) has been

se

t.

FUNCTIONAL DEFI

NIT

IONS FOR CDP1854A

TERMINALS

~

1

0DE

I

SIGNAL: FUNCTION

vDD:

P

os

itive supply voltage

MOD

E

SE

L

ECT

(MODc):

A higll·level voltage

at

this

input

selects

MODE I

operation.

VSS:

Ground

CHIP SELECT 2 (CS2):

A

lo

w·lcvcl voltage at

th

is

input ll>gether with

CS I and

CS

3 selects

th

e COPI 8S4A

UA

RT

.

RECEIVER

BUS

(R BUS 7 · R

BUS

0):

16

Receiver parallel data

outputs

(may

be

ex

·

ternally connected to corresponding tran

smit

·

tcr bus terminals).

INTERRUPT

(IN

T):

A low·lcvel voltage

al

this

output

indicates

the

p1escncc

of

one

of

more

of

the interrupt con·

ditions listed in Table 2.

FR

A

MI

NG

ER

ROR

(FE)

:

A

high-level voltage

at

this

outpu

t indicat

t!S

t

hat

th

e 1eceive

cl

character h

as

no

va

lid st

op

bit, i.e .. the bit fo

ll

ow

ing

th

e paii

ty

bit (if

pr

ogramme

d)

is

no

t a high·levcl volt:tgc. This

ou

tp

ut is

updated

e

ach

li

me

a chnraclcr is

transferred

10

the

Receiver Holding Register.

PARITY

ERROR

or

OVERRUN

ERROR

(PE{OE):

A hig)l·lcvcl voltage

at

this

output

indicat

es

that either

the

PE

or

OE b

it

in the Sll1Us

Register

ha

s been set (see Status Register Bit

Assi

gnme

nt

, Fig.

4)

.

R

EG

ISTER SELECT (RSEL):

Th

is

Input is used to choose either

the

Control

/S

tatlls Register (high input)

or

the

transrnltter{receiver data registers (low

input)

according 10 the

lruth

table

in

Table

I.

Do not sale this PDF !!!

- SERVICE 1

- 7, S bit 3

- "" 4

- BLOCK DIAGRAM 5

- Circuit 6

- I : Data 7

- Do not sale this PDF !!! 7

- AEGULATOA 8

- • G1 • 9

- INTERRUl'T 10

- LSI Discription 11

- 00 125 100 125 12

- 00 125 12

- ' 13

- PDF !!! 14

- = I) and 15

- II' 16

- 5 - JOO 17

- Do not sale this PDF !!! 18

- 10 the 19

- 7. IC PIN CONNECTION 20

- <> 21

- "' 22

- . " '• 25

- ~;:;=::::rr-~ 26

- PARTS GUIDE 27

- > Cl 29

- <' 30

- XBBSD26P 31

- '-" 32

- NI< 33

- CORPORATION 36

(89 strony)

(89 strony)

(210 strony)

(210 strony) (11 strony)

(11 strony) (14 strony)

(14 strony) (15 strony)

(15 strony)

(28 strony)

(28 strony)

Komentarze do niniejszej Instrukcji